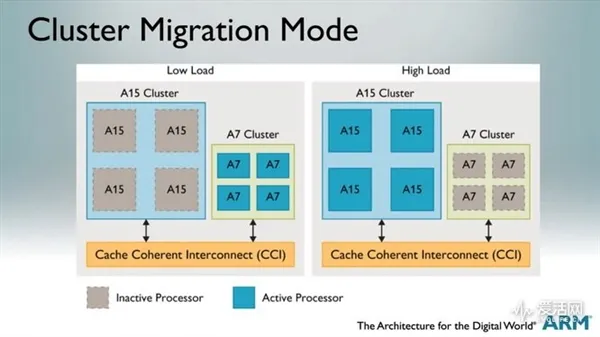

在2011年时ARM为Cortex处理器带来一项革新——big.LITTLE(以下简称bL)架构,它允许Cortex处理器拥有两种不同的核心,核心不同性能有高低,相同核心组成一个簇,轻负载下运行性能差但省电的核心,高负载下运行高性能,兼顾节能与性能。

然而bL疗效没有想象中的好,今年3月份ARM为bL拿出终极补丁DynamIQ,随着Cortex-A75/55发布,关于DynamIQ更多细节披露出来了,它真的能挽救bL么?

早于ARM处理器借智能手机崛起前,x86处理器就实现了双核心,更早面对如何平衡多核心下性能与功耗的问题,Intel、AMD最终实现方式都是独立开关每一个核心、控制每个核心频率/电压。

因此在bL出现之时受到质疑,实际效果也没想象中理想,首先是智能手机不像PC有大量文本操作, 纯粹轻负载任务不多,LITTLE难以发挥所长,其次是手机对多核心支持很差,同簇下各个核心不能单独休眠、调整,因此自主研发能力的强的高通、苹果都没有完全紧跟bL架构。

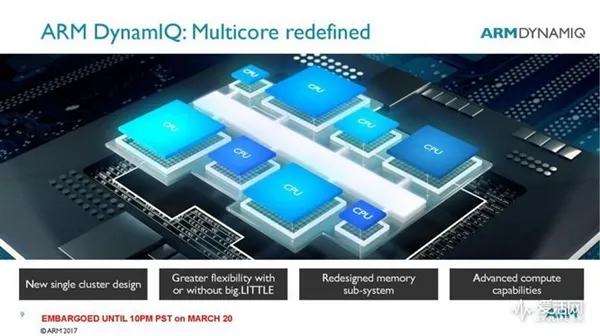

DynamIQ出现算是给bL打补丁,而且是一个超级补丁。DynamIQ先是提高了bL架构的灵活性与扩展性,它允许最多8个CPU核心构成一个簇(Cluster),单个处理器最多可实现32个簇,这样一个处理最多可以拥有256个核心,并可通过CCIX总线扩展到1000处理器。

而且簇内每一个核心可以单独开关、调整频率/电压,能效表现更加,甚至制造商是可以将不同核心(目前仅支持Cortex–A75与Cortex-A55)以不对等的数量放到一个簇内,可以Cortex-A75×3 Cortex-A55×5,也可以Cortex-A75×1 Cortex-A55×7,兼顾成本与性能。

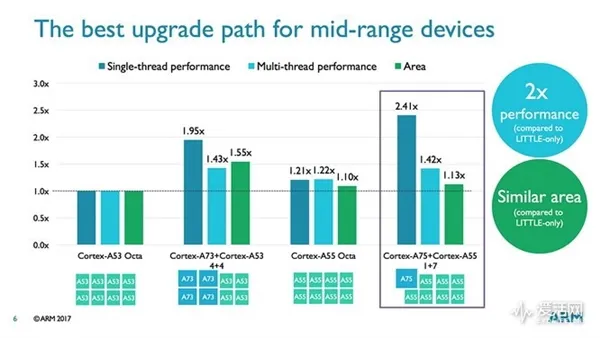

假若8个Cortex-A53核心的处理器面积、单线程性能多线程均为1X(LITTLE下),采用今天流行的Cortex-A73×4 Cortex-A53×4的bL架构后,能以1.55X面积换取1.95X单线程性能以及1.43X的多线程性能,用DynamIQ技术实现的Cortex-A75×1 Cortex-A55×7架构,只需1.13X面积就能换来2.41X单线程性能与1.42X多线程性能。ARM这组数据虽然把新核心性能提升加入其中,但考虑到巨大提升,新结构性价比还是非常高的。

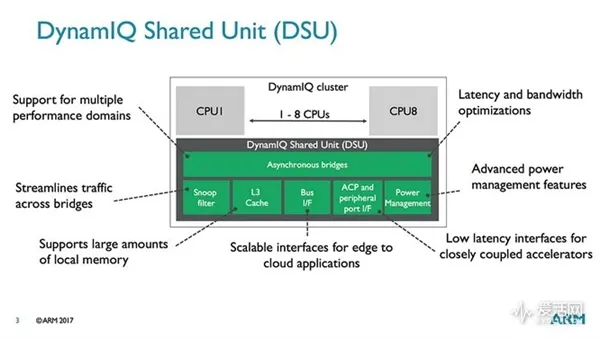

不过如此复杂的架构会带来一个问题,如何调度这些核心呢,ARM在8个核心间加入了DynamIQ Shared Unit (DSU)控制单元 。

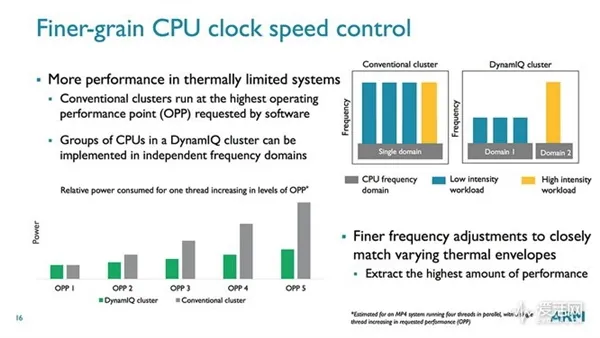

DSU能够使用CCI、CCN或是CMN不同总线技术,把CPU与SoC里其它单元(GPU、Modem、内存)高速连接起来;它拥有4MB三级缓存,能以动态方式分配缓存给每个核心,比如说Cortex-A75×1 Cortex-A55×7下,可以将3MB缓存分配给A75核心,剩下7个A55核心共享1MB缓存,甚至可将三级缓存交给GPU等单元使用,灵活性非常高;最重要的是它还负责控制簇内每个CPU核心开关,频率高低,电压大小,是控制CPU性能与功耗的关键。

在设计DynamIQ之时ARM还考虑到冗余需求,比如说汽车,相比智能手机汽车对可靠性、冗余度要求高出不少,DynamIQ允许多个簇通过CCIX连接在一起,这样处理器就可以分布在汽车不同位置,当发生交通意外一个簇受损时DynamIQ技术可以调用出备用处理器,保证汽车正常运转。

有了DynamIQ加持的big.LITTLE架构犹如CCI500相对CCI400的进步,相似名字下是质的不同,不过Cortex-A75、Cortex-A55刚刚要发布,ARM处理器要迎来这一飞跃最快也得2018年了。